# IMPROVEMENT OF PLC-BASED DATA ACQUISITION SYSTEM FOR BEAM LOSS MONITORS OF THE J-PARC MAIN RING

Shigenobu Motohashi <sup>A)</sup>, Makoto Takagi <sup>A)</sup>, Jun-ichi Odagiri <sup>B)</sup>, Norihiko Kamikubota <sup>B)</sup>, Noboru Yamamoto <sup>B)</sup>, Shuei Yamada <sup>B)</sup>, Hidetoshi Nakagawa <sup>B)</sup>, Dai Arakawa <sup>B)</sup>, Yoshinori Hashimoto <sup>B)</sup> and Takeshi Toyama <sup>B)</sup>

A) Kanto Information Service (KIS)

8-21 Bunkyouchou, Tsuchiura, Ibaraki, 300-0045

B) High Energy Accelerator Research Organization (KEK)

1-1 Oho, Tsukuba, Ibaraki, 305-0801

#### Abstract

A data acquisition system of the beam loss monitor of J-PARC Main Ring consists of the combination of Programmable Logic Controller (PLC). The system needs the high speed response to an external trigger. So we use high speed data acquisition modules to get output data from the beam loss monitor. Triggered by an external trigger pulse, the system begins to acquire the data with some pre-defined intervals by the signal which the system itself generates. We use the new type of a CPU module of PLC, in which an embedded EPICS system on the Linux OS. With the new type of a CPU module, the data acquisition system becomes simpler. This paper reports the state of development and the result in operation.

# J-PARC主リングのビーム・ロス・モニタのデータ収集システムの改良

## 1. はじめに

大強度の陽子加速器であるJ-PARC主リングのオペレーションにとって、ビーム・ロス・モニタの果たす役割は大きい $^{[1]}$ 。主リングには総計316台のガス・チェンバー型のビーム・ロス・モニタが設置され、主リング全体にわたるビーム・ロスの空間分布とともに、各測定点での加速サイクル内での時間構造がモニタされる。このためのデータ収集システムとして、これまでProgrammable Logic Controller (PLC)  $^{[2]}$ をベースにしたシステムが用いられてきたが、今回、制御ソフトウェアの保守性と性能の向上のため、PLCのCPUを通常のシーケンスCPUから

EPICS OPI

Ethemet

EHemet

EPICS IOC PLC

Ethemet

PLC

(A) (B)

図1:BLMのシステム構成 (データ収集システム)

LinuxをOSとして搭載したCPU(F3RP61)への置き換えを行った。本稿では、まず次節において通常のシーケンスCPUを用いた場合の従来の実装について述べ、第3節ではF3RP61を使ったときの実装について報告する。

## 2. シーケンスCPUによる実装

## 2.1 システムの構成

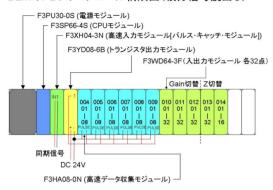

図1(A)に、PLCのCPUとして通常のシーケンスCPUを用いた場合のシステム構成を、図2に、図1(A)の場合のPLCモジュールの構成を示す。ビーム・ロス・モニタ本体からの出力は、専用の処理回路で積分され、その積分値を図2のPLCの高速データ収集モジュールで読み出し、その都度、上位のVME計算機に転送する。全数で316台のビーム・ロス・モニタからの信号は、8ユニットのPLCシステムが分担して処理する(1ユニットあたり最大48点)。

図 1 (A) の VME 計算機上では、EPICS の Input/Output Controller (IOC) のコア・プログラムが 実行されており、PLCから届いたデータはEPICSのレコードとして保持され、Operator Interface (OPI) となる上位計算機からのアクセスを可能にしている。 [3]

## 2.2 データ収集シーケンス

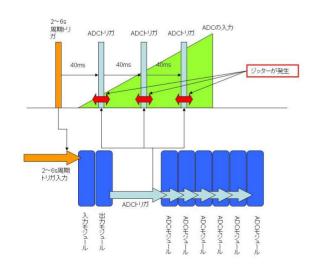

各測定点(ビーム・ロス・モニタ)における加速サイクル内での時系列データを取得するため、上記PLCは数十ミリ秒のインターバルを置きながら予め指定された回数の測定を繰り返す(図3参照)。一連の

シーケンスを開始するタイミング信号(2~6秒周 期)は、PLCのパルスキャッチ・モジュール (F3XH04-3N)に入力される。これにより、高速入力 モジュールからシーケンスCPUに割り込みがかかる。 その結果、CPU上のラダー・プログラムの割り込み 処理ルーチンが実行され、一連のデータ収集シーケ ンスが開始される。ラダー・プログラムの中では データ収集シーケンスの測定間隔の定時性を保証す るため、センサ・コントロール・ブロック (SCB) を使用している。200マイクロ秒の定周期で実行さ れるSCBの中でスキャン回数のカウントを続け、 データ収集間隔の経過を待つ。データ収集タイミン グが到来すると、SCBの中でデジタル出力モジュー ル(F3YD08-6B)の出力リレーをONし、この出力が高 速データ収集モジュール(F3HA08-0N)のAD変換開始 信号への入力として使われる。

#### BLMのPLCのモジュール構成図(積分信号読出し)

図 2: BLMのモジュール構成図 (データ収集システム)

予め指定された回数のデータ収集が終わると一連のデータ収集シーケンスは終了し、次の加速サイクルの開始を告げるタイミング信号がパルスキャッチ・モジュールに入力トリガされるまで待機する。

図3:データ収集シーケンス

## 3. F3RP61による保守性と性能の改善

### 3.1 従来のシステムの問題点

図1(A)に示すシーケンスCPUとVME計算機を IOCとして使用する構成のデータ収集システムは平 成20年5月のJ-PARC主リングのコミッショニング開 始以来、約半年間運用された。この運用では以下の ような問題点が見出された。第一に、シーケンス CPU上で実行されるラダー・プログラムが複雑であ り、維持・保守が困難であった。これはラダー・プ ログラムで行う処理が、外部からの信号により起動 され、その後の処理のタイミング生成をSCBの中で カウントアップするカウンタで行うなど、元々PLC が得意とする通常のシーケンス処理とは異質なもの であることによる。また、ソケットを使用したネッ トワーク通信をラダー・プログラムで実現している ことも可読性、保守性を損なう結果となっている。 第二に、図1(A)に示される通り、処理がPLCとIOC に分散しているため、不具合があった場合の調査が 難しかった。不具合の調査に際しては、まず問題が IOC側、PLC側、あるいはネットワーク通信の何れ に起因するものであるのか、を切り分けるところか ら始める必要があり、この段階で多くの時間を費や す必要があった。

#### 3.2 F3RP61によるシステムの簡素化

これらの問題を解決するため、平成20年12月に新 たに市場で入手可能となったCPUモジュール、 F3RP61を導入してシステムの更新を行った。 F3RP61はLinuxをOSとして採用したことにより、そ の上で直接、EPICSのコア・プログラムを実行する ことができる<sup>[4][5]</sup>。すなわち、F3RP61は、それ自身 がIOCとして機能することができる。F3RP61をCPU として使用した場合のシステムの構成を図1(B)に 示す。CPUモジュール以外のPLCモジュールについ ては、通常のシーケンスCPUを使用した場合と何ら 変わらない。図2において、単にCPUモジュールを F3RP61-2Lで置き換えた構成になる。図1(A)と(B) の二つの構成を比較した場合、PLCユニットの範囲 に限れば単なるCPUの置き換えに過ぎないが、シス テム構成全体としてみた場合には、PLCとIOCに 分されていた機能を、IOC一つにまとめたという点 において、根本的な違いがある。

この簡素化により、以下のメリットが得られる。 第一に、ラダー・プログラムを使わずにデータ収集 の処理を実装できるようになる。具体的には、この 目的に必要とされる処理に特化したEPICSのデバイス・サポートを実装することになる。デバイス・サポートはC言語で記述するため、ラダー・プログラムに較べてきめ細かい処理を柔軟に記述できる。第二に、データ収集はPLCのバス上で済み、ネットワーク越しの転送が不要となる。これによりシステムの信頼性が向上する。第三に、処理がIOC (F3RP61)に集中するため、不具合が生じたときの問題の追及が容易になる。

#### 3.3 データ収集時のジッターの測定

上述したようにF3RP61をIOCとして使用することによるシステムの簡素化には大きなメリットがあるが、データ収集のタイミングのジッターに関して留意する必要がある。通常のシーケンスCPUを使用する場合、データ収集のタイミングにはSCBの最小スキャンタイム程度(400マイクロ秒程度)の不定性が生じることは不可避であるが、逆に、最悪でもその程度に収まることが保証される。これに対し、F3RP61上でデータ収集を実行する場合にはLinux

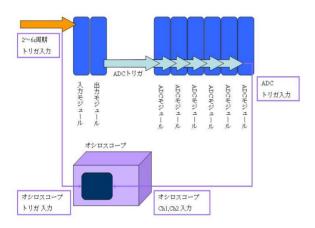

図4:ADCジッター測定のセッ トアップ

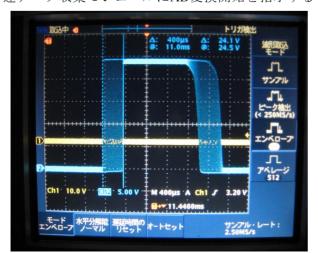

カーネルのリアルタイム応答性により決まる不定性が生じるが、この場合の最悪値を推定することは容易ではない。F3RP61のLinuxの場合、カーネル2.6のプリエンプション機能(カーネル・モードで実行中のプロセスから処理を横取りする機能)が有効にされているため、一定のリアルタイム応答性は期待できるものの、その程度については実測による評価が必要である。そこで実機で使用するPLCと同じ構成で割込応答性を測定した(図4参照)。

まず、パルスキャッチ・モジュールにトリガ信号を入力し、これによりF3RP61に割り込みを掛ける。割り込みを待って休眠するスレッドは起床すると高速データ収集モジュールにAD変換開始を指示する

図5:出力信号のジッター

ためのトリガ信号をデジタル出力モジュールに出力する。パルスキャッチ・モジュールへの入力を起点として、出力信号が出力されるまでの時間をオシロスコープで観測した。十分な時間のデータをため確認したところ、図5に示される通り、ジッターは約400マイクロ秒に収まっており、通常のシーケンスCPUの場合に期待し得るジッターと同程度である。

#### 3.4 運用実績

F3RP61を使ったシステムは平成21年4月からのMRの運転で実用に供され、本稿執筆時(平成21年7月)まで順調に稼働している。

## 4. 結論

J-PARC主リングのビーム・ロス・モニタのデータ収集システムを、F3RP61を使って更新した。データ収集を行うPLCユニットのCPUモジュール上で直接、EPICSのコア・プログラムを実行することにより、ハードウェア構成が簡素化され、ソフトウェアの維持・保守が格段に容易になった。データ収集タイミングのジッターを測定し、通常のシーケンスCPUを使用した場合に期待される値より悪くならないことを確かめた。更新後のシステムは平成21年4月からのMRの運転で実用に供され、これまでのところ問題なく動作している。

図6:BLMのPLCモジュール

## 参考文献

- J. Odagiri, WP68, Proceedings of the 4th Annual Meeting of Particle Accelerator Society of Japan, Wako, Aug. 1-3, 2007

- [2] http://www.fa-m3.com/jp/

- [3] http://www.aps.anl.gov/epics/

- [4] S. Odagiri, et al., "Application of EPICS on F3RP61 to Accelerator Control", in this meeting

- [5] M. Takagi, et al., "Control of the J-PARC Slow Extraction Line Based on Embedded EPICS", in this meeting