## Multipoint T-maps for Vertical Test of the Superconducting Accelerator Tubes

Hiromu Tongu $^{A)}$ , Yoshihisa Iwashita $^{A)}$ , Hiroshi Fujisawa $^{A)}$  Hiromi Sato $^{B)}$ ,

Hitoshi Hayano <sup>C)</sup>, Ken Watanabe <sup>C)</sup>, Yasuchika Yamamoto <sup>C)</sup>

A) Institute for Chemical Research Kyoto University Gokasho, Uji, Kyoto, 611-0011

B) The Institute of Physical and Chemical Research (RIKEN), Hirosawa 2-1, Wako-shi, Saitama, Japan 351-01

C) High Energy Accelerator Research Organization (KEK), 1-1 Oho, Tsukuba, Ibaraki, Japan 305-0801

#### Abstract

The temperature mapping (T-map) system for inspection of cavity interior surface is developed for the vertical test. T-map system can find heat sources that may be caused by defects on the superconducting cavity. The purpose of our studies on T-map is to realize a high special resolution and easy installation of the sensors. The production yield of such cavities would be improved by using such a high resolution T-map system. The preliminary test of cryogenic temperature by the T-map system is reported.

# 超伝導加速管の縦測定における超多点温度マップ

#### 1. はじめに

ILC第 1 期計画では電子、陽電子をそれぞれ250GeVまで加速し500GeVで衝突させる。そのために平均加速勾配35MV/mの加速空胴が電子、陽電子あわせて約15000台が必要となる。ILC線形加速器では図1に示すニオブ製の9セルL-band超伝導加速空胴の採用が決まっている。製作数量が多く生産効率をあげるため日本、アメリカ、ヨーロッパで生産のための研究が進められている。

加速勾配の上限は空胴内の表面状態に大きく依存していると考えられ、高圧超純水洗浄や電解研磨などの表面処理法により高い加速勾配が得られるようになってきている。しかし依然として空胴製作の歩留まりは芳しくなく、ILCの超伝導加速空胴の開発、製作において空胴内の表面状態を非破壊で観察、検査する必要がある。

## 2. 研究目的

加速勾配を制限する原因の1つは空胴内面に付着した数ミクロンのゴミやキズ、数百ミクロンの凹凸などの欠陥による局所的熱源からのクエンチと考えられている。そのため平均加速勾配35MV/mを実現するためにはミクロンオーダーで空胴の内表面管理をする必要がある。加速空胴内を観察、検査を行う方法として高分解能小型カメラを利用し表面を観察する装置[1]が利用されているが、超伝導加速空胴に

図1 ニオブ製9セル超伝導加速空胴

高周波電力を注入して行う縦測定試験(図2)にて十分な密度で温度マッピングできれば発熱場所を測定し、空胴内表面の欠陥場所を確定することが容易となる。しかし、この温度上昇マッピングは単純ではあるが実装が大変なシステムである。本研究では超伝導加速空胴の縦測定において非破壊検査を全セル同時、かつ手軽に運用できるシステムを研究開発し、その結果をILC加速空胴の生産において歩留まりの向上に生かすことを目的としている。

### 3. T-map

#### 3.1 測定システム

本研究のT-mapシステムの特徴である超多点測定と簡便実装を実現するためにセンサーに酸化ルテニウムのチップ抵抗を用い、短冊状フレキシブル基盤を用いて空胴外壁に接触させる方式を採用した(図3)。この温度センサーの高密度化により測温感度と測定位置精度の向上、さらに容易に装備できるデバイスにより空胴内表面の欠陥検査時間の短縮を期待する。

図2 高エネルギー加速器研究機構での縦測定

図3 温度センサー基盤 フレキシブル基盤上に配列したチップ抵抗面 を空胴外壁に接触させ裏のコネクタとマルチ プレクサ基盤と接続する。

#### 3.2 抵抗值選択

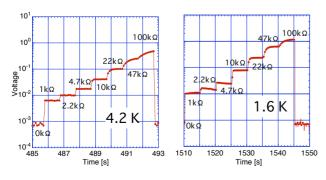

理化学研究所で昨年度行った温度センサーとして 使用するチップ抵抗の抵抗値を選択するための実験 にて $1-100k\Omega$ まで7個の抵抗について測定した。

図5 酸化ルテニウムチップ抵抗の極低温での出力電圧 測定温度は左図4.2K、右図1.6K。

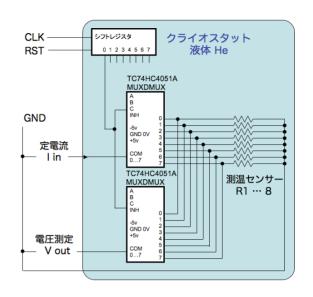

図4 T-map回路

チップ抵抗に定電流を流し、抵抗の電圧を測定する。クライオスタットからのケーブル数を減らすためCOMSアナログマルチプレクサとチャンネル切替えのためのシフトレジスタをクライオスタット内に設置して測定を行う。

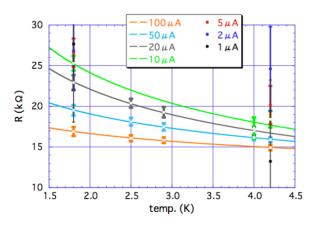

図 5 に示すように抵抗値が大きいほど出力電圧が大きく、1.6K/4.2Kの温度変化に対する感度は $10k\Omega$ より小さい値では1.5倍、 $10k\Omega$ 以上では2-2.5倍となり、抵抗値が大きいほうが感度は良い。しかしながら大きな抵抗値では時定数が大きくなり立ち上がりの信号出力がなまっているのがわかる。これはセンサーの自己発熱の影響などを含めた電流電圧特性の非線形性が効いいていると思われる。これらのことから $10k\Omega$ のチップ抵抗の採用を決めた。

### 4. 測定結果

#### 4.1 切替え周波数とセンサー入力電流

図4のシステムと図3のセンサー基盤を用いて7月に高エネルギー加速器研究機構 STFにて9セル縦

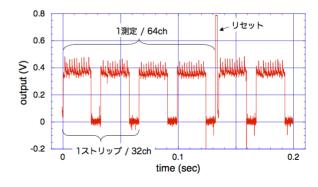

図 6 出力信号波形 1測定は $64(16\times4)$ チャンネルで16chの内4ch はショート。クライオスタット内温度4K のとき切替え周波数250Hz、センサー入力 電流 $20\,\mu$  Aで測定。

図7 出力信号の切替え周波数依存性 クライオスタット内温度4K、入力電流20  $\mu$  Aで測 定。通電直後から電圧が下がるのはチップ抵抗の 自己発熱と考えられる。

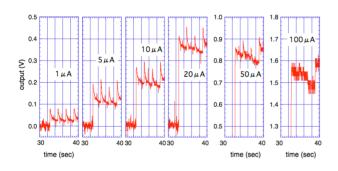

図8 出力信号のセンサー電流依存性 クライオスタット内温度4Kのとき切替え周波数500Hzで測定。50,100 $\mu$ Aのグラフの縦軸はオフセットしている。

図9 温度センサー(抵抗 $10k\Omega$ )の感度。 電圧信号から換算した抵抗値を入力電流ごとのグラフで示す。抵抗値は測定を行った48個のセンサー出力の平均値。

測定と同時に行ったT-map動作試験のセンサー出力 波形が図6である。また、図7に入力電流固定し チャンネル切替え周波数を変えた結果を示した。 500Hzでは3chの信号ピークが明確だが、ピーク後か ら抵抗値が下がり出力信号が弱くなっているのはチップ抵抗の自己発熱の影響と思われる。自己発熱の抑制、および測定時間の短縮を考慮し周波数をがると2.5kHzからは立上がり時間が足りずピークであると2.5kHzからは立上がり時間が難しくなっている。次にチャンネル切替え間が難している。次にチャンネル切替え間でとしている。次にチャンネル切替え間でといる。では一人力電流を変えて測定した出力信号がが、同時電池が大きいるようである。自己発熱を考慮すると通電電流は少ない方が良いが、 $1\mu$  A以下では信号がノイズに埋もれる可能性もある。

#### 4.2 測定結果の考察

今回の測定に使用した48個のチップ抵抗の出力平均から極低温環境での抵抗値の変化を図9にまとめた。 $1,2,5\mu$  Aの低電流側ではデータ点が少なく不明だが $10\mu$  A以上の入力電流では温度にしたがって抵抗値が非線形に大きくなっているのがわかる。入力電流が少ない方がセンサーとしては感度が良いといえる。この主たる原因は抵抗の自己発熱と考えている。しかしながら図9に示すように入力電流 $5\mu$  A以下ではエラーバーが大きく、チップ抵抗個々のばらつきが顕著に現れている。これらのことから10k  $\Omega$  チップ抵抗を温度センサーとして用いる場合は入力電流 $10-20\mu$  A、切替え周波数(サンプリングレート)1-2kHzが推奨値と考える。

## 5. まとめ

今回の測定で安価なチップ抵抗が極低温環境で温度センサーとして使用が可能であり、またケマレクであり、これではいたCMOSアナログ回路では、一次のできたのコンパクリケロができた。回路ノイブの自己を熱力できた。の追加動作では、一次の主にないが、今後の追加動をでは、一次の主にないが、一人力電流などでである。この方式のT-mapを採用すると対すとりはできた。この方式のT-mapを採用ると対すというである。大ップ抵抗と空胴間の熱にしてに、シ、チップ抵抗と空胴間のというが、があげられる。固定は、シ、チップ抵抗の実装を問到しつが、があげるが、本方に現状の実をである。

### 参考文献

[1] Y. Iwashita, et al., "Development of high resolution camera for observations of superconducting cavities", Phys. Rev. ST Accel. Beams 11, 093501 (2008)